지난 10여년 동안 엔지니어들은 반도체 집적회로 줄이기 경쟁이 언제쯤 막을 내릴지 주의깊게 지켜봐 왔다. 이들은 물리법칙에 의해 전통적인 반도체 트랜지스터 게이트의 크기를 5나노미터(nm)이하로 만들기가 어렵다는 사실을 알고 있었다. 5nm라면 현재 최신품으로 시중에 나와있는 20nm짜리의 4분의 1에 불과한 것이다.

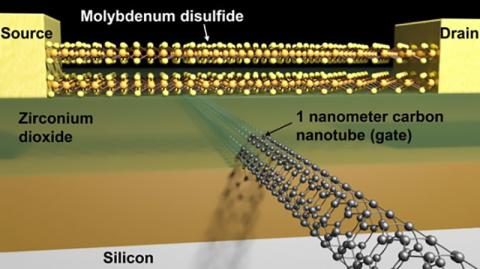

그러나 법칙이란 깨어지거나 도전 받기 마련. 미국 에너지부 산하 로렌스 버클리 국립연구소(Berkeley Lab) 알리 재비(Ali Javey ) 교수팀은 1nm짜리 게이트를 가진 트랜지스터를 만들어냈다고 과학저널 ‘사이언스’(Science) 7일자에 발표했다. 1nm는 10억분의 1m로, 사람 머리카락 한 올의 굵기는 5만nm다.

이번 연구에는 UC 버클리의 제프 보커( Jeff Bokor), 첸밍 후(Chenming Hu) 교수, 스탠포드대의 필립 웡(H.S. Philip Wong) 교수와 함께 한인 과학자인 김문제(Moon Kim) 텍사스대(댈러스) 교수도 공저자로 참여했다.

“5nm 이하 게이트는 업계서 생각조차 안해”

버클리 랩 재료과학부 전자재료 프로그램 책임연구자인 재비 교수는 “우리는 지금까지 보고된 것 중 가장 작은 트랜지스터를 만들었다”며, “게이트 길이는 트랜지스터의 크기를 결정하는 요소로, 우리는 알맞는 재료를 선택해 전자를 줄여 넣을 수 있는 많은 공간이 있는 1nm 게이트 트랜지스터를 입증해 냈다”고 밝혔다.

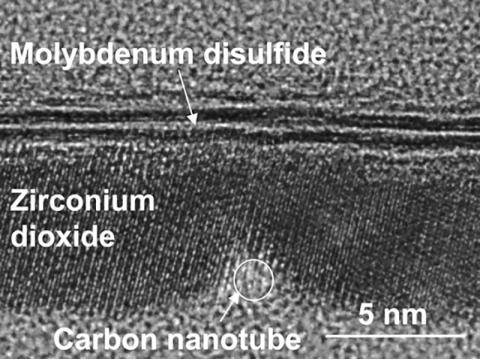

이 같은 성공은 탄소 나노튜브와 자동차 엔진 윤활유에 쓰이는 이황화 몰리브덴(MoS2)을 사용함으로써 가능했다. 이황화 몰리브덴은 LED와 레이저, 나노 규모의 트랜지스터, 태양전지 등 수많은 곳에 응용할 수 있는 잠재력을 지닌 재료로 꼽힌다.

새로운 차세대 트랜지스터 개발에 따라 노트북이나 모바일폰 같은 각종 전자제품에 쓰이는 반도체 집적회로의 트랜지스터 밀도 즉 성능이 매 2년마다 두 배로 늘어난다는 ‘무어(Moore)의 법칙’이 여전히 유효하게 됐다. 최근 빅데이터, 가상현실(VR), 증강현실(AR), 인공지능(AI), 클라우드, 자율주행차 등 4차 산업혁명의 키워드가 등장하며 이를 뒷받침할 대용량 메모리 기술도 더욱 절실한 시점이 됐다. 그러나 반도체 미세공정이 한계를 보이면서 ‘무어의 법칙’도 폐기되는 것이 아니냐는 시각이 없지 않았다.

논문 제1저자인 재비 교수 연구실의 수제이 디사이(Sujay Desai) 대학원생은 “반도체 산업계에서는 오랫 동안 5nm 이하의 게이트는 작동하지 않을 것이라고 생각해 아예 고려조차 하지 않았었다”며, “이번 연구는 5nm 이하의 게이트에 대한 관심을 일깨운다”고 말했다. 그는 “재료를 실리콘에서 이황화 몰리브덴으로 바꿔 1nm 길이의 게이트를 만들 수 있었고, 스위치와 같이 잘 작동했다”고 덧붙였다.

실리콘에서 이황화 몰리브덴으로

트랜지스터는 소스(source)와 드레인(drain), 게이트 등 세 개의 터미널로 구성돼 있다. 전류가 소스로부터 드레인으로 흐르며, 이 흐름은 주어지는 전압에 반응해 스위치가 켜지고 꺼지는 게이트에 의해 조절된다.

실리콘이나 이황화 몰리브덴 모두 크리스탈 격자 구조를 가지고 있으나 실리콘을 통해 흐르는 전자는 이황화 몰리브덴에 비해 가볍고 저항을 덜 받는다. 이 같은 일은 게이트가 5nm나 그보다 길 때 일어난다. 길이가 그보다 작을 때는 터널링 효과라 부르는 양자역학 현상과 게이트 장벽이 더 이상 전자가 소스에서 드레인 터미널로 흘러가는 것을 막을 수가 없다. 디사이는 “이는 트랜지스터를 끌 수가 없다는 것을 의미하며 전자들을 제어할 수 없다”고 말했다.

이황화 몰리브덴을 통해 흐르는 전자는 좀더 무겁기 때문에 게이트 길이가 더 짧아도 제어가 가능하다. 이황화 몰리브덴은 0.65nm 두께로 얇게 축소가 가능하고, 전기장에서 에너지 축적력을 반영하는 유전율(誘電率)도 더 적다. 게이트 길이가 1nm로 축소됐을 때 전자의 질량 이외에 이 두 가지 특성이 트랜지스터 안에서의 전자 흐름 조절을 증진하도록 돕는다.

‘개념 증명’ 연구 실용화가 과제

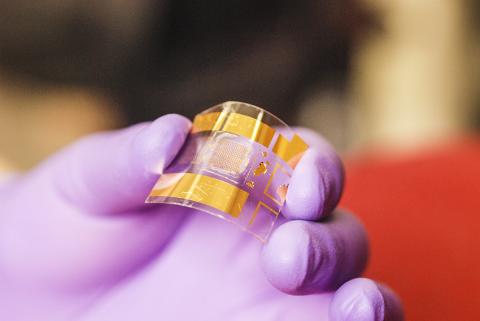

반도체 재료로 이황화 몰리브덴을 채택한 다음에는 게이트를 만들 차례. 1nm 구조를 구축하는 것은 실제로 쉬운 일이 아니다. 이같이 작은 규모에서는 전통적인 회로기판 인쇄 기술이 제대로 작동하지 않기 때문에 연구팀은 직경 1nm짜리의 속이 빈 원통형 카본 나노튜브를 선택했다.

이런 과정을 거쳐 트랜지스터를 만든 후 전기적 특성을 측정하자 연구팀은 전자 흐름이 효과적으로 제어되는 것을 확인할 수 있었다.

재비 교수는 “이 일련의 작업을 통해 세계에서 가장 작은 트랜지스터를 선보이게 됐다”며, “그러나 이번 연구는 개념 증명 수준으로 트랜지스터를 마이크로칩에 장착하지도 않았고, 수많은 재현 실험도 거치지 않았으며 트랜지스터의 기생저항을 줄이기 위한 자기 정렬 제조과정도 아직 개발하지 않았다”고 밝혔다.

그는 “그럼에도 불구하고 이번 연구는 트랜지스터 게이트가 5nm에 한정되지 않는다는 사실을 보여주었다는 점에서 중요하며, 연구 결과를 활용해 제품을 만들어내면 ‘무어의 법칙’이 한 동안은 생명력을 이어갈 것”이라고 말했다.

- 김병희 객원기자

- kna@live.co.kr

- 저작권자 2016-10-07 ⓒ ScienceTimes

관련기사

뉴스레터

뉴스레터