저항변화 메모리 소자. 고밀도와 고집적, 저전력의 성질로 인해 차세대 메모리 소자로 주목받고 있는 저항변화 메모리 소자는 전기적 신호를 통해 전기저항을 높이거나 낮추면서 저항상태에 따라 정보를 기록할 수 있는 특징을 갖고 있다.

현재 산업계에서 비휘발성 메모리 소자로 널리 사용되는 것에는 '낸드 플래시(NAND flash)' 소자가 있다. 기업들도 이를 연구하는 데 매우 활발한데, 일본 기업 '도시바(Toshiba)'에서는 기존의 평면 구조인 낸드 플래시를 3차원으로 적층해 면적당 기억 용량을 크게 향상시킬 수 있는 구조를 제안했으며, 삼성전자는 수직 적층형 낸드플래시 소자(VNAND) 양산에 성공했다.

경쟁력 있는 기업에 의해 계속 연구되는 낸드플래시. 저항변화 메모리 소자가 이러한 낸드 플래시와 경쟁하기 위해서는 3차원 적층 구조를 개발하는 것이 필수다.

"종이 여러 장 겹치는 원리 생각하면 되죠"

국내 연구진이 저항변화 메모리 소자를 3차원 적층하는 데 필요한 과제를 제안해 주목을 받고 있다. 황철성 서울대 재료공학부 교수팀이 3차원 적층 구조에서 예상되는 문제점과 극복방안들을 체계적으로 연구, 기존 연구팀에서 발표한 129편의 연구내용을 종합해 발표했다. 종합된 내용으로 국내 과학계가 3차원 적층 구조를 어떻게 연구하는 게 효과적일지 그 기준을 제시한 것이다.

목표성능과 제작기준 등을 언급한 이번 논문은 그 성과를 인정받아 재료과학 분야의 국제학술지인 '어드밴스드 펑셔널 머티리얼스(Advanced Functional Materials)' 지 온라인 판에 게재됐으며 '주목받는 논문(Feature Article)'으로 선정되기도 했다.

단위면적당 메모리의 용량을 높이기 위해서는 집적도를 높이는 게 필요하다. 하지만 집적도를 향상시키기 위해서는 마치 고층빌딩처럼 메모리 소자를 3차원적으로 적층하는 기술이 관건이다.

"현재 메모리를 비롯한 대부분의 반도체는 2차원적인 평면구조입니다. 예컨대 넓은 종이 위에 글자를 쓰는 것과 비슷하다고나 할까요. 만일 더 많은 내용을 종이에 쓰고 싶다면 종이를 키우거나 글자를 작게 써야 하겠죠. 지금까지의 반도체는 주로 글자를 작게 쓰는 방향으로 발전해 왔습니다. 한계가 있을 수밖에 없죠. 이와 마찬가지로 반도체도 작게 만드는 데는 한계가 있습니다. 때문에 적층방식으로 넘어가야 한다는 주장이 제시됐어요. 적층방식이란 이름 그대로 '쌓는 것'을 말합니다. 종이를 여러 장 겹쳐 책을 만드는 모습을 상상하면 되겠네요."

그러나 반도체는 책과 달리 여러 층을 쌓는 과정이 매우 어렵다. 기존의 평면 구조에서는 없던 문제들도 발생하기 때문에 결코 쉬운 과제라고 할 수 없었다. 황철성 교수는 "그러한 이유 때문에 문제점과 해결 방안을 정리해서 논문을 발표했다"고 이야기 했다. 그렇다면 기존의 3층 적층 방식 저항변화 메모리 소자가 갖고 있던 문제점은 무엇일까.

"일단 첫 번째 문제는 전류가 누출되는 현상입니다. 각각의 메모리에는 조금씩 새는 전류가 있는데 메모리 용량이 커질수록 이렇게 새는 전류가 더욱 많이 모이겠죠. 모인 전류에서는 또 다시 전류가 샐 것이고요. 결국 조금씩 누출되는 전류가 모여 많은 전류가 또 다시 누출된다는 게 문제였습니다. 마치 하나의 수도꼭지에서 물이 한 방울씩 누수 된다고 할 때 이러한 수도꼭지가 수천, 수만 개 모인다면 많은 물이 새는 것과 비슷한 원리죠. 저항변화 메모리 소자에서 이런 수도꼭지와 같은 역할을 하는 것을 ‘선택 소자’라고 합니다. 이번 연구에서는 여러 가지 형태의 3차원 적층 방식의 저항변화 메모리 소자에서 새는 전류의 크기를 계산하고 이를 막을 수 있는 선택 소자를 적층방식에서 어떻게 구현할 것인가에 대해 정리했습니다."

황철성 교수가 제시한 또 다른 문제점은 복잡하고 대면적을 차지하는 연결구조가 필요하다는 점이었다. 여전히 2차원 평면구조인 다른 반도체 회로들과 3차원 적층 구조를 연결하기 위해서는 특정한 연결구조가 필요한데 이는 매우 복잡하고 차지하는 면적 역시 매우 넓다. 때문에 연결구조를 단순화 할 수 있는 방법이 필요했다.

"연구를 통해 단순한 연결구조의 방법을 정리하고 비교했습니다. 반도체 공정 중 '식각공정'이라는 것이 있는데 이 공정을 줄이면 제조비용을 크게 줄일 수 있어요. 적층 방식에 따라 한 층 한 층 올릴 때 마다 식각공정을 하는 경우도 있고, 일단 여러 층을 쌓아 놓고 한 번의 식각공정으로 만드는 경우도 있죠. 당연히 후자가 기술적으로 어렵습니다. 하지만 제조비용을 아낄 수 있으니 많은 사람들이 후자의 방식을 지향하고 있습니다. 저희 팀의 이번 연구는 후자의 방식을 사용할 때 필요한 메모리 소자의 구조와 제조 공정 기술 등에 대해 내용을 정리하고 있습니다."

황철성 교수가 언급한 '후자'의 방식은 식각 공정을 한 번만 거치면 된다. 이 '한 번' 이라는 것이 많은 효율을 가져다주지만, '한 번'의 공정으로 여러 층을 만들어야 하기 때문에 매우 좁고 긴 구멍을 이용해야 하는 어려움이 있다.

"이러한 구조는 수직으로 반듯한 구멍을 만드는 일도 매우 어렵고 그 안에 메모리 반도체 물질을 균일하게 채우는 것은 더욱 어렵습니다. 뿐만 아니라 기존에는 이러한 구조를 만들었을 경우 얼마만큼의 전류가 샐 것인지 예측하고 어떤 선택 소자가 필요한 지에 관한 연구가 부족했죠."

적층의 두 가지 방식, 쌓기와 배열하기

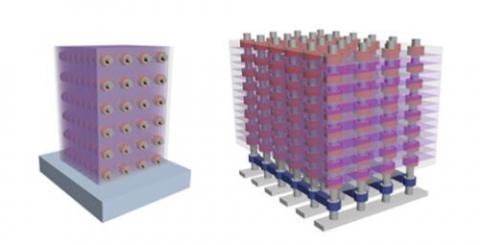

3차원 적층구조의 저항변화 메모리 소자를 만드는 방법에는 크게 두 가지가 있다. 쌓는 것과 배열하는 게 바로 그것으로, 전자는 기존 평면구조의 크로스 바 어레이 구조를 반복해 쌓는 방법이다. 이는 기존의 평면구조를 그대로 사용할 수 있다는 장점이 있지만 적층 횟수에 비례해 사진 식각공정 횟수도 증가한다는 단점이 있다. 식각공정 횟수가 증가하면 제조비용이 크게 증가한다는 문제가 발생한다.

다른 하나는 기존의 평면구조를 옆으로 눕혀 마치 책을 꽂듯 크로스 바 어레이 구조를 옆으로 배열하는 방법이다. 기판에 수직방향인 배선을 단 한 번의 사진 식각공정으로 만들 수 있지만 수직방향의 배선제작을 위해 종횡비가 큰 구조를 제작해야 하는 어려움이 있다.

"쌓아 올리는 공정은 매 층마다 따로따로 식각 공정을 통해 평면 구조와 거의 동일한 메모리 구조를 만드는 과정입니다. 수직하게 배열하는 구조는 수직으로 구멍을 만드는 공정이기 때문에 수직 배열 방향의 구조를 한 번의 식각 공정으로 만들 수 있다는 차이가 있습니다. 이것만 보면 수직 배열이 기술적으로 어려울 뿐, 더 좋은 구조라고 생각 할 수 있습니다만 사실은 쌓아 올리는 구조만의 장점도 있습니다. 수직 구조와 달리 수평으로 쌓아 올리는 구조는 각 층을 독립적으로 만들 수 있어요. 때문에 한 층에서 새는 전류의 양만 조절하면 전류가 새는 문제를 해결할 수 있습니다. 반면 수직 구조의 경우 각 층이 유기적으로 연결돼 있기 때문에 새는 전류들도 층마다 모두 합쳐져 상대적으로 더 많은 양의 전류가 새는 문제가 있죠. 이처럼 각각 일장일단이 있기 때문에 어느 한 구조가 무조건 우세하다기 보다는 목적에 맞는 구조를 선택하는 것이 중요하다 할 수 있겠습니다."

풀리지 않았던 난제를 일목요연하게 정리한 황철성 교수. 그렇다면 그는 어떤 계기에서 이번 연구를 시작한 걸까. 질문을 받은 그는 보다 포괄적이고 근본적인 대답을 했다. 과학계에서는 한 문제에 대해 많은 사람들이 연구를 진행하는데 각자 다른 방식으로 자신들의 해결책을 제시하기 때문에, 언젠가는 이를 정리하는 시간이 필요하다고 여긴 것이다.

"국내·외 여러 그룹에서 발표하는 논문들을 접하다 보면 연구자마다 서로 다른 방식으로 문제를 정의하고 각자 자신들의 해결책을 제시하는 걸 알 수 있어요. 때문에 연구 결과를 이해하기 위해서는 매번 밑바닥부터 살펴봐야 하고 서로 다른 연구들 간의 상관관계를 이해하기 어려운 경우가 많았습니다. 그러다보니 3차원 적층 저항변화 메모리라는, 하나의 주제로 관련 연구들을 모아 정리해보는 것이 좋겠다는 생각이 들었어요. 여러 연구 내용들을 근본 동작 원리에 따라 분류하고 정리하면 각각의 장단점도 쉽게 파악할 수 있고 앞으로의 연구가 나아가야 할 방향도 잘 알 수 있겠다는 생각이 들어 작업을 시작했습니다."

물론 연구과정 중에 크고 작은 어려움도 많았다. 황 교수는 "논문 내용이 저널에 맞지 않는다는 지적이 많았다"고 회고했다. "아무래도 이번 논문에서 상당 부분을 할애하고 있는 내용은 적층 구조를 어떻게 만들 것인가에 대한 내용이에요. 그러다 보니 기존 재료 분야의 연구자들에게는 생소한 내용이었던 것 같습니다. 논문의 내용도 재료분야 저널에는 맞지 않는다는 지적을 많이 받았죠. 하지만 재료와 구조는 떼려야 뗄 수 없는 관계입니다. 구조를 알지 못하면 재료를 연구할 수 없고, 재료를 알지 못하면 구조 또한 연구할 수 없어요. 어떤 구조를 만들지 알고 있어야 그에 적합한 재료를 선택할 수 있고, 혹은 무엇을 재료로 선택할지에 따라 그에 적합한 구조가 선택되기도 합니다. 이러한 점을 들어 잘 설득한 결과 재료분야의 최고 권위 학회지인 '어드밴스드 펑셔널 머티리얼스(Advanced Functional Materials)' 지에서 주목 받는 논문(feature article)로 발표할 수 있었죠."

황 교수가 제안한 이번 연구의 가장 큰 특징은 기존의 여러 연구 그룹에서 독립적으로 연구된 결과를 하나의 큰 틀 안에 포함시켜 정리했다는 점이다. 이를 통해 각각 구조들의 장단점을 비교할 수 있게 됐고 각 구조에 가장 적합한 메모리와 선택 소자의 재료를 예상할 수 있었다.

"저희 팀의 이번 연구가 하나의 가이드라인 역할을 할 것으로 기대하고 있어요. 3차원 적층 저항변화 메모리분야에 새로이 관심을 갖는 연구자들에게 좋은 방향을 제시해 줄 수 있지 않을까요. 저는 지금까지 약 10년이 넘는 시간 동안 저항변화 메모리에 관해 연구했습니다. 그동안 크고 작은 성과를 거둬왔죠. 하지만 몇 년 전부터 시작된 3차원 적층 메모리에 관해서는 이제 막 시작하는 단계라고 생각합니다. 그렇기 때문에 이번 연구는 그동안 진행한 연구의 마침표가 아닌 쉼표로써, 새로운 단계로 나아가기 위한 디딤돌이 돼야 한다는 생각이 들어요. 연구를 토대로 앞으로는 3차원 적층 저항변화 메모리 소자의 연구에 더욱 박차를 가해 향후 3~4년 이내에 본 논문에서 제시한 최적의 구조를 실제로 구현 할 수 있는 핵심 기술을 개발하고 싶습니다."

- 황정은 객원기자

- hjuun@naver.com

- 저작권자 2014-07-31 ⓒ ScienceTimes

관련기사

뉴스레터

뉴스레터